Whatapp/WeChat: 008618589033832

Skype: Sannyduanbsp

Apakah tujuan kapasitor berganda pada cipBekalan kuasaPin?

Sebagai jurutera elektronik diketahui bahawa kapasitor umumnya berfungsi empat fungsi utama: decoupling, gandingan (menyekat DC sementara membenarkan AC lulus), penapisan, dan penyimpanan tenaga. Hari ini, saya akan memberi tumpuan kepada menerangkan fungsi decoupling.

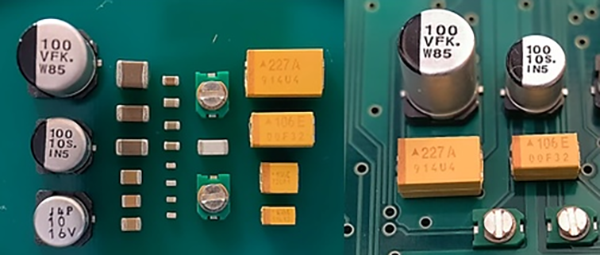

Jenis biasa kapasitor decoupling

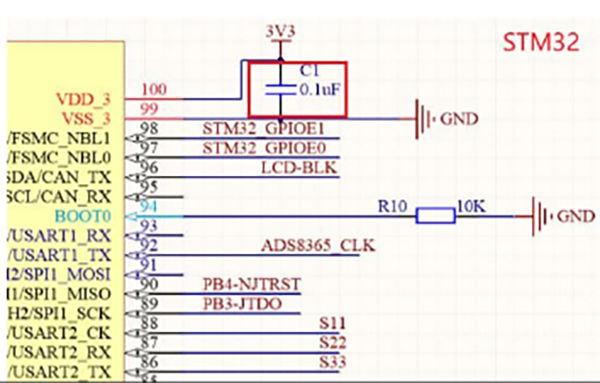

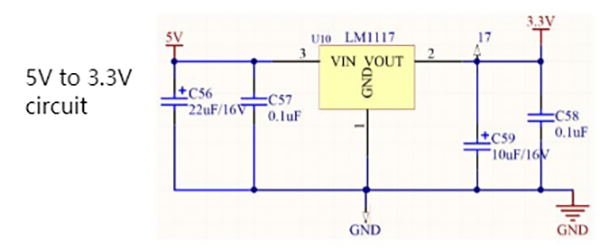

Imej di atas menunjukkan skema separa konfigurasi bekalan kuasa minimum STM32 siri. MCU ini memerlukan lima kereta api kuasa 3.3V, yang biasanya dibekalkan oleh LDO (pengawal selia rendah), seperti LM1117.

Mengapa kapasitor decoupling diperlukan

Walaupun LDOS umumnya memberikan voltan yang lebih stabil berbanding denganPenukar DC-DC(contohnya, TPS5430), walaupun voltan yang dibekalkan LDO dapat menunjukkan ketidakstabilan untuk cip berprestasi tinggi. Untuk menangani ini, kami meletakkan kapasitor decoupling berhampiran pin bekalan kuasa cip. Kapasitor ini menyerap bunyi AC frekuensi tinggi dari bekalan kuasa, mengalihkannya ke tanah, dengan itu memastikan cip menerima voltan DC yang stabil dan boleh dipercayai. Untuk prestasi yang optimum, kapasitor decoupling mesti diletakkan sedekat mungkin ke pin cip.

Kenapa kapasitor 0.1μF biasa digunakan?

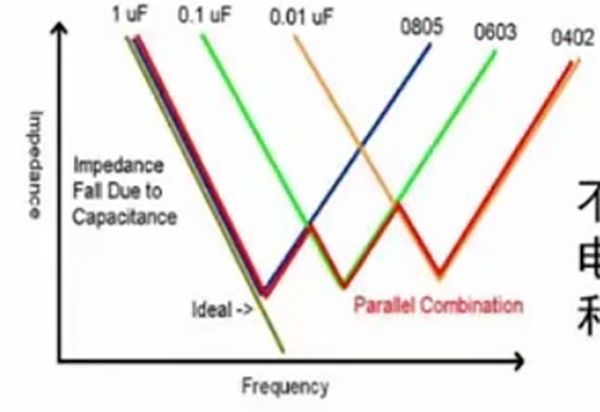

Apabila mengkaji integriti kuasa, kita sering menganalisis kapasitor seperti ini, pada frekuensi yang lebih rendah, kapasitor terutamanya berfungsi sebagai penapis. Walau bagaimanapun, apabila kekerapan meningkat, komponen induktif kapasitor menjadi penting dan akhirnya menguasai. Di luar ambang frekuensi tertentu, keberkesanan penapisan kapasitor berkurang. Ini bermaksud bahawa difrekuensi tinggi, kapasitor tidak lagi bertindak sebagai kapasitor "tulen". Ciri -ciri penapisan sebenar kapasitor digambarkan dalam lengkung di bawah:

Dari lengkung, penapisan ideal berlaku di titik terendahimpedanslengkung (impedans minimum). Walau bagaimanapun, apabila kekerapan meningkat, kapasitor 0.1μF menjadi kurang berkesan berbanding dengan kapasitor 0.01μF. Pada frekuensi yang lebih tinggi, nilai kapasitans yang lebih kecil (misalnya, 0.001μF) diperlukan untuk penapisan optimum.

Penyelesaian: Kapasitor selari

Untuk menangani batasan ini, banyak reka bentuk litar menggunakan pelbagai kapasitor selari dengan nilai kapasitansi yang berbeza. Dengan menggabungkan kapasitor nilai yang berbeza -beza, julat kekerapan penapisan yang berkesan diperluaskan, memastikan penindasan bunyi yang lebih baik merentasi spektrum yang lebih luas. Pendekatan ini membolehkan prestasi penapisan yang lebih baik ke atas frekuensi yang lebih luas.

Shenzhen Anke PCB Co., Ltd

Masa Post: Mar-07-2025